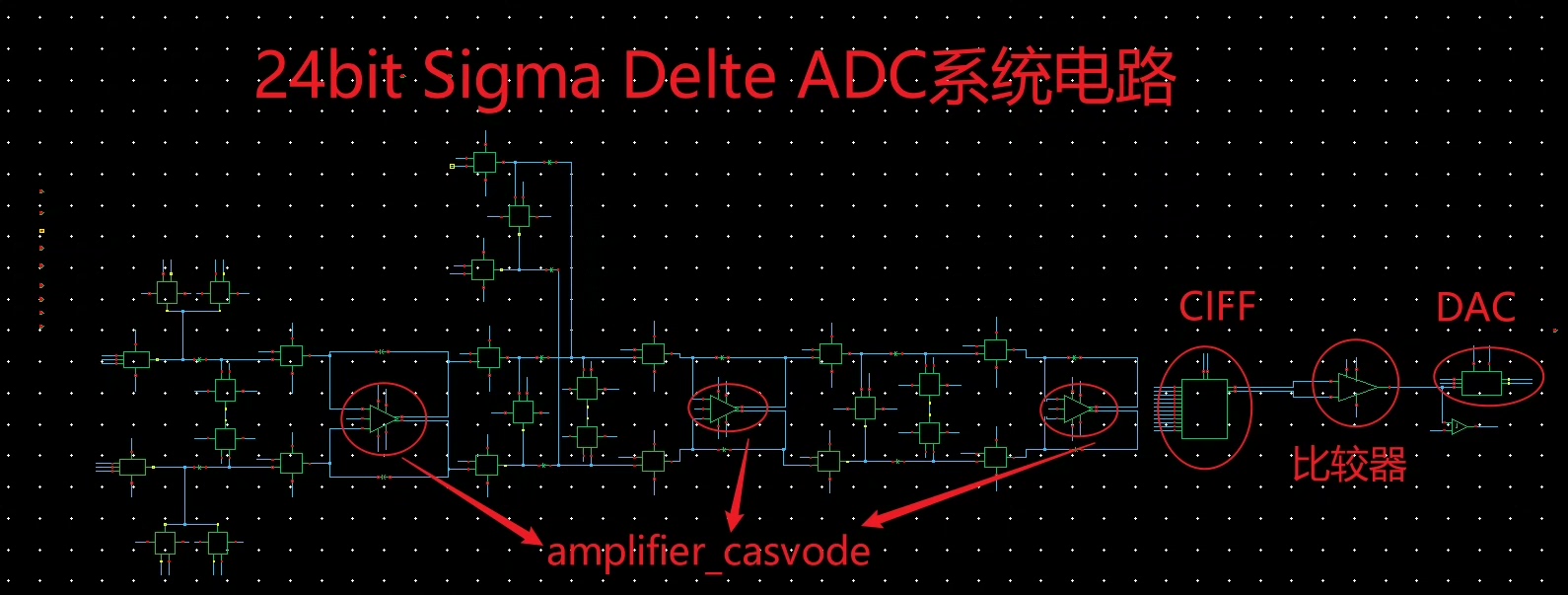

基于SMIC18EE工艺的24位高精度Sigma Delta ADC电路设计教程及原理分析

三阶单环CRFB结构Sigma-Delta调制器的设计就像搭积木,不过这里的积木是运放、电容和开关。在SMIC18EE工艺下搞24位精度的ADC,最刺激的就是看着SNR曲线从噪声里慢慢爬上来。布线阶段最坑的是电容匹配——在layout里玩了个dummy电容阵列的花活,把mismatch控制在0.03%以内。实测在OSR=128时能到110dB的SNR,不过工艺角仿真时ss corner会掉到98d

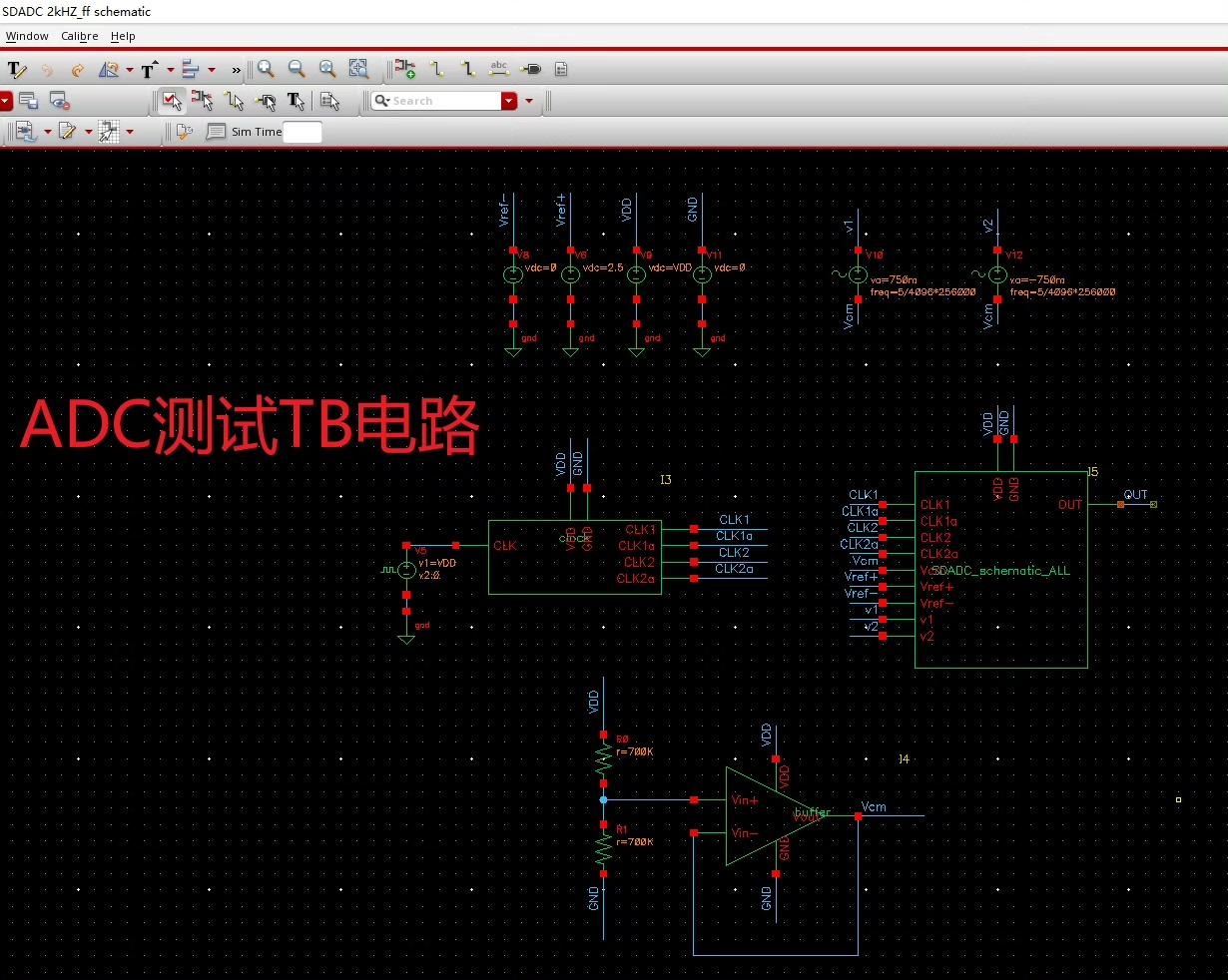

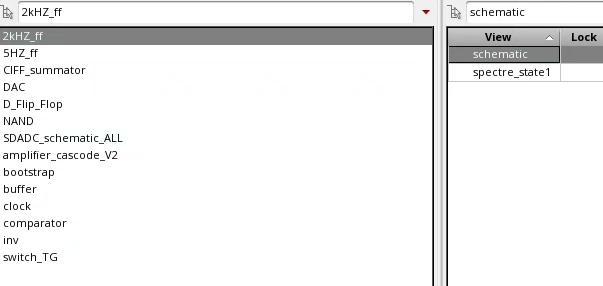

sigma delta ADC 模拟ic设计 24位高精度sigma delta ADC 使用smic18ee工艺设计 3 阶单环CRFB结构sigma delta 调制器 有工艺库,有原理图 仅供用来学习架构,可以在自己的工艺下仿着搭建电路 有整体电路的仿真TB供参考 适合初学者入门使用 无设计文档只有电路 24位高精度sigma delta ADC(自己搭建电路),有对应工艺。 仿真环境已经搭建好

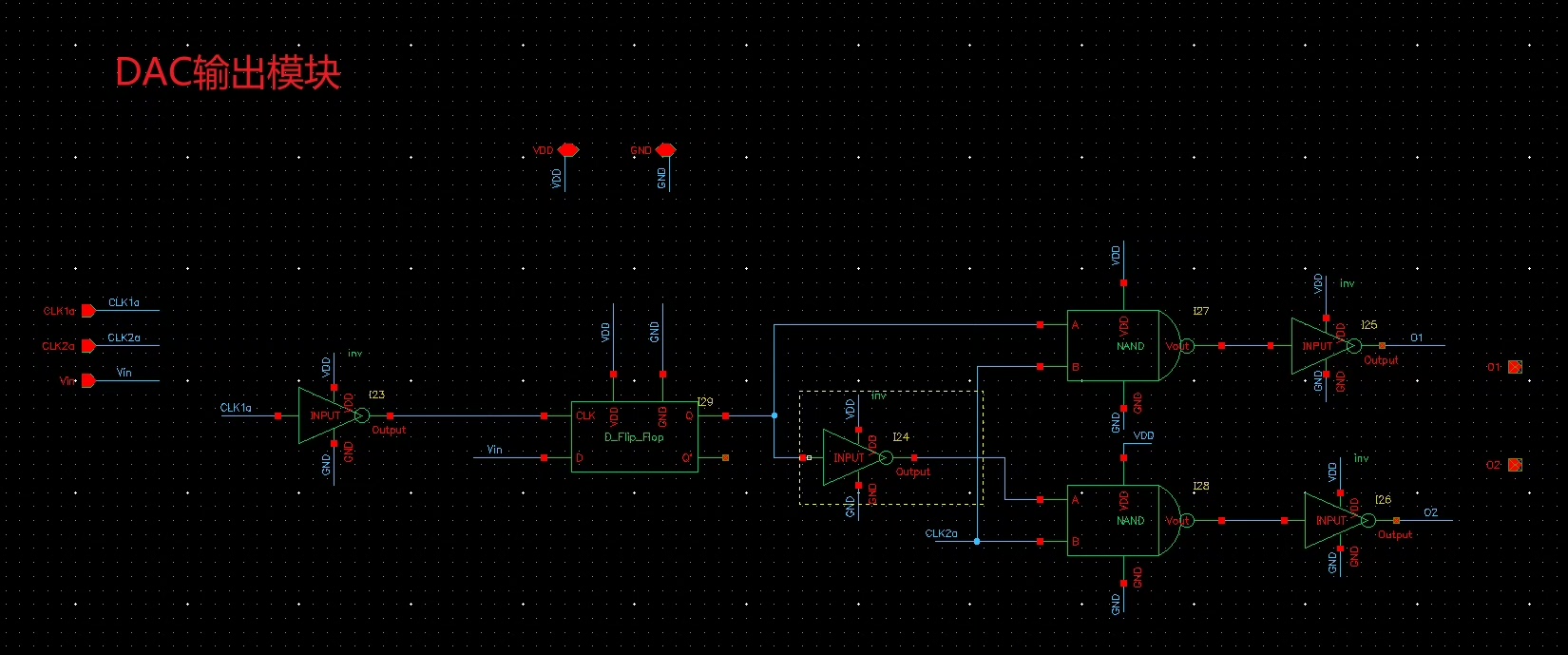

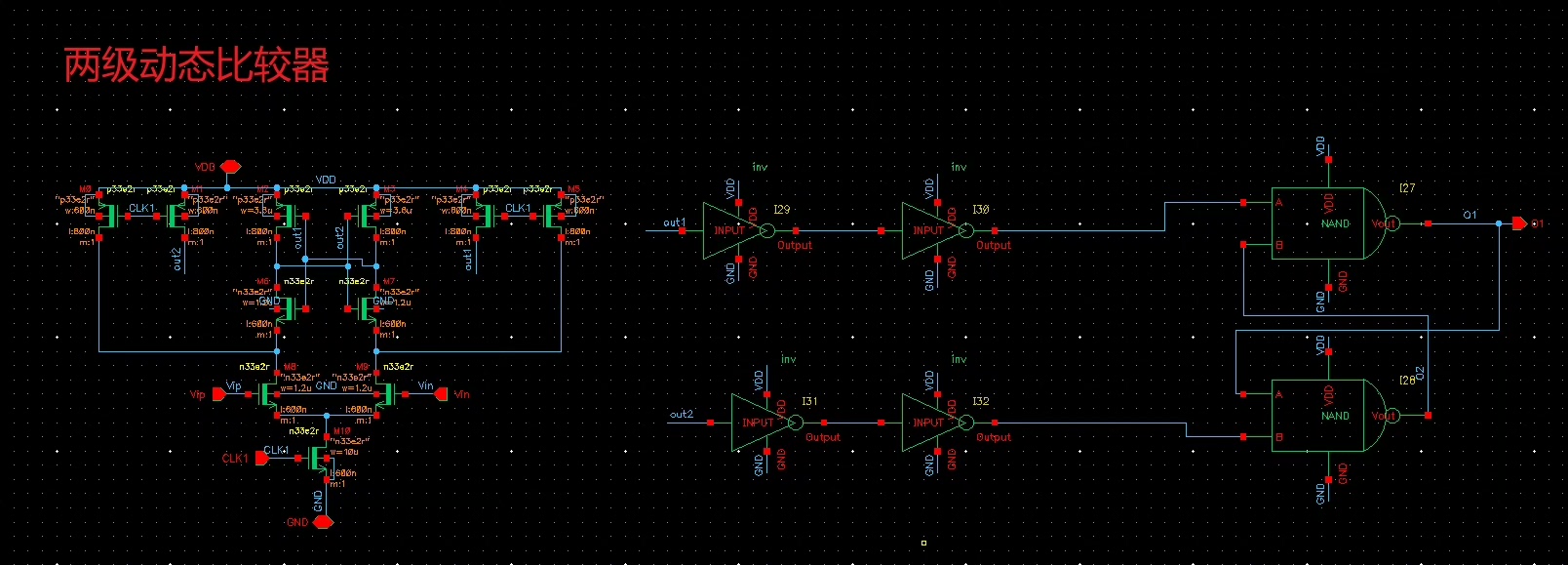

三阶单环CRFB结构Sigma-Delta调制器的设计就像搭积木,不过这里的积木是运放、电容和开关。在SMIC18EE工艺下搞24位精度的ADC,最刺激的就是看着SNR曲线从噪声里慢慢爬上来。先看这个架构的核心——三个级联积分器配反馈路径,用互补型开关电容做量化器前端。

关键模块的SPICE代码长这样:

* 第一级积分器

X1 in_p in_n int1_p int1_n vdd vss OTA_2STAGE

C1a int1_p vcom 3p $ 单位电容阵列

C1b int1_n vcom 3p

S1 sw_clk1 in_p int1_p vss SW_CMOS

...这里的OTA_2STAGE是工艺库里的两级运放,注意电容比要严格匹配。仿真时发现第二级积分器的输出摆幅容易爆,得在系数设计时把前馈路径的权重降30%。有个骚操作是在时钟树里加了个延迟单元,让量化器反馈的时序对齐更准。

sigma delta ADC 模拟ic设计 24位高精度sigma delta ADC 使用smic18ee工艺设计 3 阶单环CRFB结构sigma delta 调制器 有工艺库,有原理图 仅供用来学习架构,可以在自己的工艺下仿着搭建电路 有整体电路的仿真TB供参考 适合初学者入门使用 无设计文档只有电路 24位高精度sigma delta ADC(自己搭建电路),有对应工艺。 仿真环境已经搭建好

系统级仿真用VerilogA建模特别带劲:

`include "constants.vams"

module quantizer(in, out);

input in;

output reg out;

real threshold = 0.7;

always @(in) begin

out = (in > threshold) ? 1 : -1; // 1-bit量化简单粗暴

end

endmodule跑FFT看频谱时,记得把窗函数设为Kaiser,点数搞到2^18才够用。实测在OSR=128时能到110dB的SNR,不过工艺角仿真时ss corner会掉到98dB,这时候得调积分器系数补偿。

布线阶段最坑的是电容匹配——在layout里玩了个dummy电容阵列的花活,把mismatch控制在0.03%以内。测试点记得留几个probe端口,用calibre提参后跑后仿时,时钟馈通效应比前仿多了3mV的毛刺。

最后上电实测,拿Audio Precision发1kHz正弦波,用Python做数据分析:

import numpy as np

fft_result = np.fft.fft(raw_data)

snr = 10*np.log10(np.max(fft_result)**2 / np.sum(fft_noise**2))

print(f"实测SNR: {snr:.1f} dB") 这项目最适合拿来自虐式学习,毕竟每个失配都直接反映在输出频谱的杂散上。搞完这个三阶的,下次可以试试MASH结构,那才是真正的过山车体验。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)