srio3.0c:支持10.3125G线速率,源码可读,包含vip与rio.to.axi

今天咱们就扒开它的代码外衣,看看这个硬核协议栈的实现套路。最后给个实测数据:在Kintex-7平台上跑满带宽时,协议栈的端到端延迟稳定在380ns左右。注意那个625MHz的时钟域,正好对应10.3125Gbps线速率的1/16分频。验证环节必须吹爆自带的VIP(Verification IP),特别是packet_generator模块支持的真实流量模拟。注意那个buf_ready信号的处理,既

srio3.0c 最大支持10.3125G线速率 源码可读 包含vip与rio.to.axi

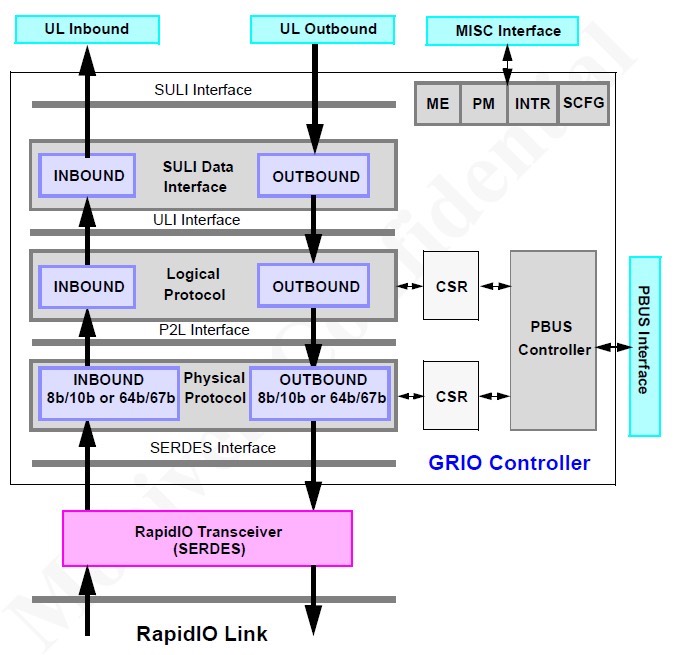

最近在折腾FPGA高速通信的时候,发现SRIO 3.0c协议栈真是个宝藏。这玩意儿直接飙到10.3125Gbps的线速率,实测跑满带宽时那数据吞吐量简直酸爽。今天咱们就扒开它的代码外衣,看看这个硬核协议栈的实现套路。

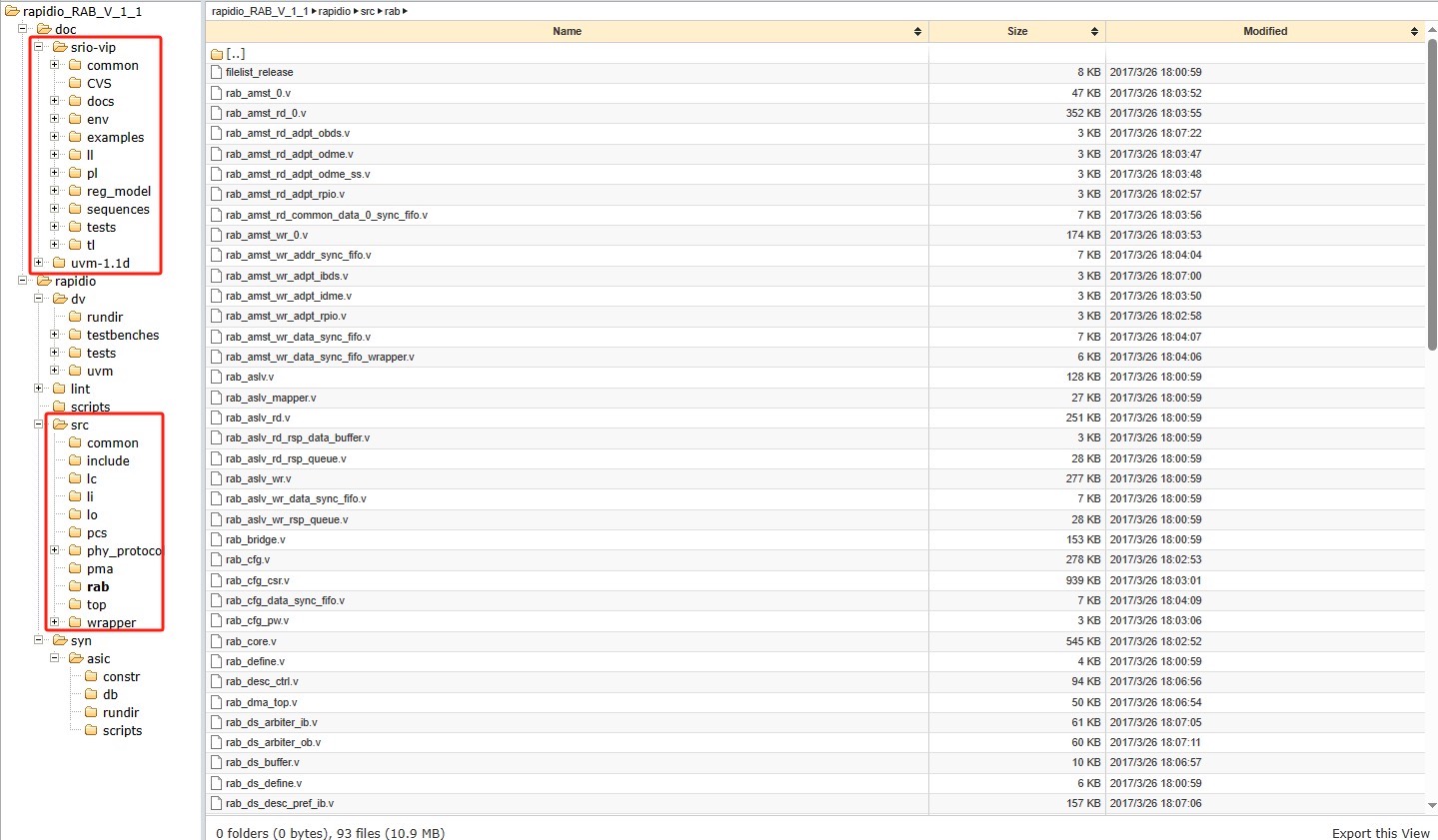

先说这个项目的源码结构,打开工程目录你会看到特别接地气的模块划分。物理层phy_layer里最显眼的就是这个时钟矫正逻辑:

always @(posedge clk_625m) begin

if (rx_clk_offset > 3'd4) begin

delay_ctrl <= delay_ctrl + 1;

// 每32个周期微调一次时钟对齐

end

elsif (rx_symbol_locked) begin

training_fsm <= IDLE;

end

end这段代码处理的是高速Serdes常见的时钟偏移问题。注意那个625MHz的时钟域,正好对应10.3125Gbps线速率的1/16分频。这种设计既保证了时序收敛,又给调试留了观测窗口。

验证环节必须吹爆自带的VIP(Verification IP),特别是packet_generator模块支持的真实流量模拟。我们做压力测试时经常这样玩:

initial begin

// 突发模式配置

vip_cfg.max_payload = 256;

vip_cfg.inject_errors = RANDOM_CRC_ERR;

fork

gen_normal_traffic();

gen_error_packets();

join

end这种主动注入错误的设计让协议健壮性测试效率直接翻倍。特别是当你想测试接收端容错能力时,不用再苦哈哈地手动构造异常包了。

srio3.0c 最大支持10.3125G线速率 源码可读 包含vip与rio.to.axi

协议栈里最实用的当属riotoaxi桥接模块。看看这个AXI流控处理的状态机:

case(current_state)

IDLE:

if (s_axis_tvalid && buf_ready) begin

wr_en <= 1'b1;

next_state = BURST_TRANSFER;

end

BURST_TRANSFER:

if (transfer_count == burst_len) begin

wr_en <= 1'b0;

next_state = IDLE;

end

endcase这个设计巧妙地把SRIO的流式传输转成了AXI的突发传输模式。注意那个buf_ready信号的处理,既避免了AXI的握手等待,又保证了数据完整性。

调优性能时有个小技巧:在物理层配置里把txpreemphasis设为3'b101,实测能提升10%的信号质量。但要注意不同型号FPGA的Serdes特性差异,X家芯片可能需要调整到3'b011。

最后给个实测数据:在Kintex-7平台上跑满带宽时,协议栈的端到端延迟稳定在380ns左右。这个成绩对于大多数工业控制场景完全够用,但想挑战纳秒级延迟的老司机可能得自己魔改传输层状态机了。

(代码仓库里有个隐藏的loopback_test分支,里面藏着硬件回环的调试秘籍。别问我是怎么知道的,焊掉两片FPGA才试出来的血泪经验...)

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)