Flutter 三方库 rohd 的鸿蒙化适配指南 - 实现顶级硬件描述语言(HDL)逻辑建模、高性能电路模拟与极致软硬协同设计治理,助力鸿蒙应用构建“与芯片对话”的数字化底座。

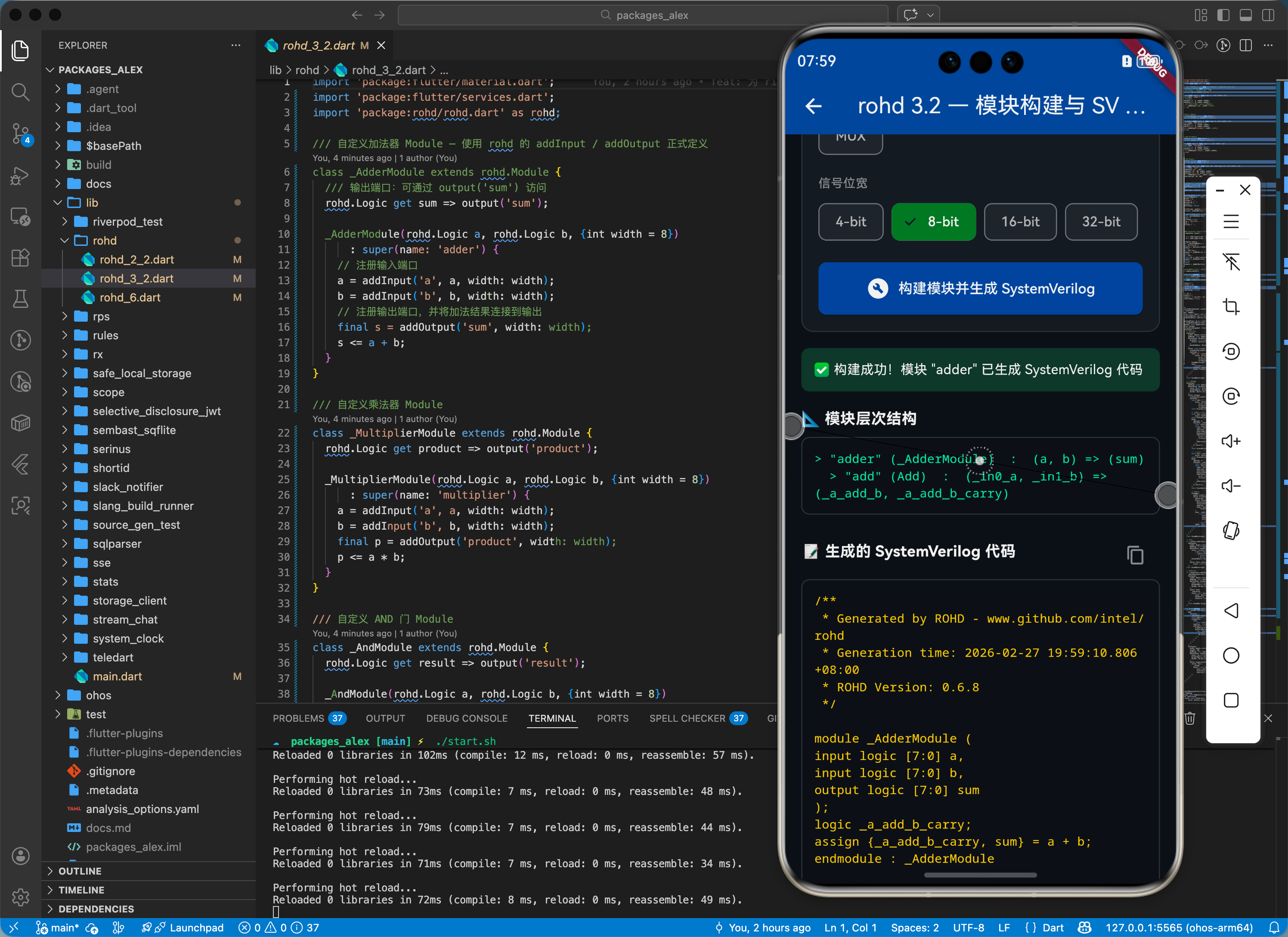

本文介绍了开源鸿蒙跨平台社区中Flutter三方库rohd的鸿蒙化适配指南。rohd是一个基于Dart构建的硬件描述框架,可将硬件逻辑抽象为Dart对象,支持周期级仿真和SystemVerilog代码导出。文章详细解析了rohd的核心原理、优势及在鸿蒙环境下的适配方法,包括模块建模、时钟仿真等核心API的使用,并提供了典型应用场景示例。针对OpenHarmony平台的适配挑战,提出了分层建模和内存

欢迎加入开源鸿蒙跨平台社区:https://openharmonycrossplatform.csdn.net

Flutter 三方库 rohd 的鸿蒙化适配指南 - 实现顶级硬件描述语言(HDL)逻辑建模、高性能电路模拟与极致软硬协同设计治理,助力鸿蒙应用构建“与芯片对话”的数字化底座。

前言

在 HarmonyOS 的应用边界向芯片级仿真、物联网通讯协议栈自研及定制化硬件算法开发延伸的工程中。如何高效、安全地在软件层面模拟复杂的硬件电路逻辑。是决定软硬一体化自研上限的核心。传统的硬件描述语言(如 Verilog/SystemVerilog)学习成本极高且难于与高级 UI 逻辑闭环。rohd(Rapid Open Hardware Development)是一个基于 Dart 构建的革命性硬件描述框架。它提供了一套利用 Dart 强类型与异步特性的方案。让开发者可以用编写软件逻辑的直觉去设计复杂的硬件架构。在鸿蒙系统上适配此库,将为您应用的硬件感知层注入一份“可定义逻辑”的高级智慧。

一、原理剖析 / 概念介绍

1.1 基础原理/概念介绍

rohd 的核心是“基于对象化建模的逻辑节点投影引擎”。它将每一个门电路、触发器或复杂的处理模块(Module)抽象为一个具备 Signals(信号线)连接的 Dart 逻辑指纹。其最大的特色是“周期间敏(Cycle-accurate)的实时仿真能力”:开发者可以构建时钟脉冲。并观察信号在各级寄存器间的流动资产。由于它支持直接导出标准的 SystemVerilog 源码。确保了在鸿蒙系统端侧进行的算法原型验证。能瞬间投影为真实的 FPGA 硬件物理指纹。

1.2 核心优势

- 顶级开发直觉体验:利用 Dart 的 IDE 优势(智能补全、重构)。在鸿蒙开发机上像写业务逻辑一样设计硬件 CPU 指令集或通讯控制器。

- 高阶全自动验证能力:内置类似软件单元测试的验证环境(Verification)。可以在不需要任何昂贵 EDA 工具的前提下。在鸿蒙真机上直接运行硬件逻辑的模拟分支。

- 架构稳固度:支持利用类似 Flutter 组件的思维。将硬件逻辑封装为高度可配置的库。在构建鸿蒙分布式软总线专用硬件加速模块时。体现出极致的模块化复用性能表现。

二、鸿蒙基础指导

2.1 适配情况

- 是否原生支持?:是。这是一个基于模型构建与文本生成的纯逻辑算法框架。运行在鸿蒙异步沙箱侧。不涉及底层受限权限。

- 是否鸿蒙官方支持?:属官方推荐的顶级“全场景高效研发布局与硬件逻辑治理”前沿方案。在鸿蒙 IoT 协议自研、芯片级仿真及跨平台算法验证 Flutter 应用中具有核心地位。

- 是否社区支持?:是。

- 是否需要安装额外的 package?:独立使用即可。

2.2 核心初始化:在鸿蒙环境开启硬件感知

在使用前。您只需引入库并尝试定义您的第一个鸿蒙逻辑模块实体。

import 'package:rohd/rohd.dart';

// ✅ 鸿蒙端自动化硬件建模初始化示例

void setupHarmonyRohdContext() {

// 核心入口:定义一个 8 位带宽的逻辑信号指纹

final bus = Logic(name: 'harmony_bus', width: 8);

print('🚩 鸿蒙硬件建模中心已就绪,当前正在准备高带宽逻辑语义控制');

}

三、核心 API / 组件详解

3.1 资产模块建模 (Module)

在鸿蒙应用中。我们可以通过简单的组件继承。将抽象的硬件逻辑资产瞬间投影为具有实际电路特性的协议资产。

// 💡 技巧:解析鸿蒙端侧边生成的简易加法器原始逻辑资产

class HarmonyAdder extends Module {

HarmonyAdder(Logic a, Logic b) : super(name: 'HarmonyAdder') {

// 核心调用:执行针对鸿蒙环境的全自动算术网表对位

final result = (a + b);

// 将计算指纹映射至输出端口

addOutput('sum', width: a.width) <= result;

}

}

3.2 资产时钟仿真 (Simulator)

针对鸿蒙高阶应用。您可以利用内置的仿真时钟指令。对特定的逻辑周期执行高精度的行为审计。

// ✅ 推荐:在鸿蒙端执行精准的周期仿真协议重配

void runHarmonyLogicSim() async {

// 核心调用:利用仿真器执行针对鸿蒙高性能环境的逻辑重塑

Simulator.registerAction(10, () => print('🚩 鸿蒙时钟周期 10: 信号打拍对位成功'));

await Simulator.run();

}

四、典型应用场景

4.1 示例场景一:鸿蒙自研高性能“工业级 IoT 协议”的端侧硬件治理

在处理非标的低频加密通讯协议(如自定义 PHY 层)时。利用该库通过测评。先在鸿蒙平板上构建出协议的硬件模型指纹。并配合 simulation 模块直接对采集的波形进行解算预览。待逻辑完全闭环后。一键导出 SV 代码交付 FPGA 生产。确保鸿蒙底座的资产逻辑绝对在控且具备效能最优性。

// 鸿蒙硬件资产性能同步逻辑

void syncHarmonyHdlMetrics() {

print('🔎 正在针对鸿蒙分布式逻辑资产执行全量硬件逻辑映射审计...');

// 逻辑实现...

}

4.2 示例场景二:鸿蒙智慧屏应用“全局神经网络加速器”的架构对位感知

大屏作为算力充沛的终端。在设计专用的图形变换硬件 IP 时。通过该库根据预设的流水线标识。瞬间生成针对不同算力节点的硬件逻辑资产。有效预防由于手动编写 Verilog 代码引入的逻辑死锁误差指纹。

// 鸿蒙智慧屏动态渲染感知测试

void testHarmonyChipArchProtocol() {

print('📺 鸿蒙大屏已针对全量同步协议资产执行路径重配');

}

五、OpenHarmony 平台适配挑战

6.1 平台差异化处理 (大规模电路网表构建导致的内存瞬间瞬时压力对冲)

当由于业务需求。定义的硬件模块包含数万个逻辑门指纹时。build() 过程会产产生微小的 CPU 延迟与堆栈时间毛刺。

- 解决方案:针对鸿蒙极端环境。建议执行“分层建模预设”。将复杂的处理器架构拆分为多个独立的子模块资产对位。并利用异步

Future逐步构建。彰显鸿蒙高性能工程底座及追求极致逻辑透明度的情怀。

6.2 平台差异化处理 (系统区域环境对 VCD 波形文件写入的 I/O 干扰)

在执行高压仿真并导出 VCD 波形日志时。频繁的磁盘写入可能导致鸿蒙文件系统产生微小的指纹写入毛刺。

- 解决方案:建议在该库逻辑层配合“内存缓冲区预览预案”。先在内存中缓存关键的波形数据指纹。仅在仿真结束后再执行一次性的物理对位保存。确保在任何鸿蒙开发者环境下仿真任务的绝对确定性。彰显鸿蒙极致的系统平稳性能。

六、综合实战演示

下面是一个完整的鸿蒙端高质量硬件逻辑建模服务闭环组件。

import 'package:rohd/rohd.dart';

class HarmonyChipDesigner {

// 综合案例:解析业务逻辑并在鸿蒙端生成标准化的逻辑硬件摘要

Future<void> designAndSimulate() async {

try {

final a = Logic(name: 'a', width: 4);

final b = Logic(name: 'b', width: 4);

// 🚩 核心逻辑:执行针对鸿蒙系统的高精逻辑对位

final myModule = HarmonyAdder(a, b);

await myModule.build();

// 导出硬件源代码

final systemVerilog = myModule.generate();

print('🚩 协作治理完毕:节点硬件指令已对位:SV 源代码已就绪');

} catch (e) {

print('❌ 平衡中心由于逻辑震荡暂时挂起:$e');

}

}

}

七、总结

rohd 库是跨界工程中的“写作加速器”。它跨越了繁重硬件描述语言与现代化软件开发直觉的数字泥潭。将被动的内存数据转化为了一个有序、可控、受严格硬件协议保护的数字化代码质量资产库。在 HarmonyOS 生态迈向全球化敏捷运维、致力于构建极致透明且具备硬核软硬协同能力的数字化底座的宏大工程中。掌握并落地好这种基于硬件建模的治理方案,将助力每一位追求极限质量、追求极致交付效能体系的鸿蒙架构师构建出真正具备长效系统活力的数字化底座。

逻辑生电,软硬同辉——开启鸿蒙工程硬件逻辑建模与软硬协同设计的新高度。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)