FPGA 中 RGMII 接口以太网:UDP、ICMP 和 ARP 协议的实现之旅

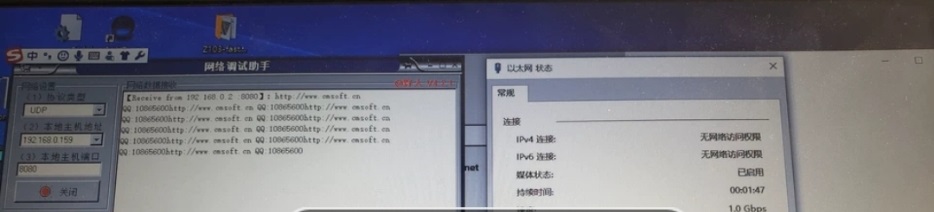

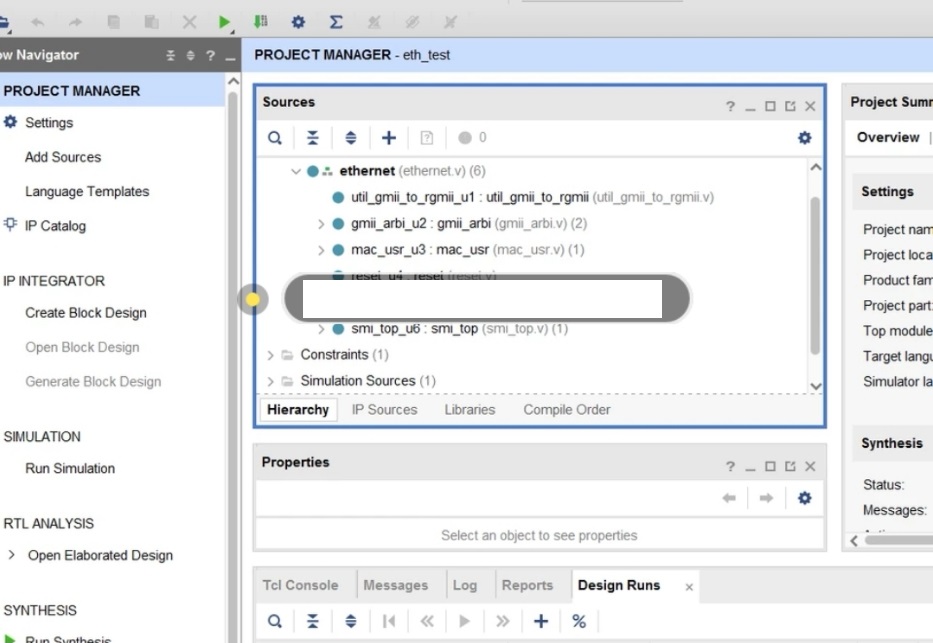

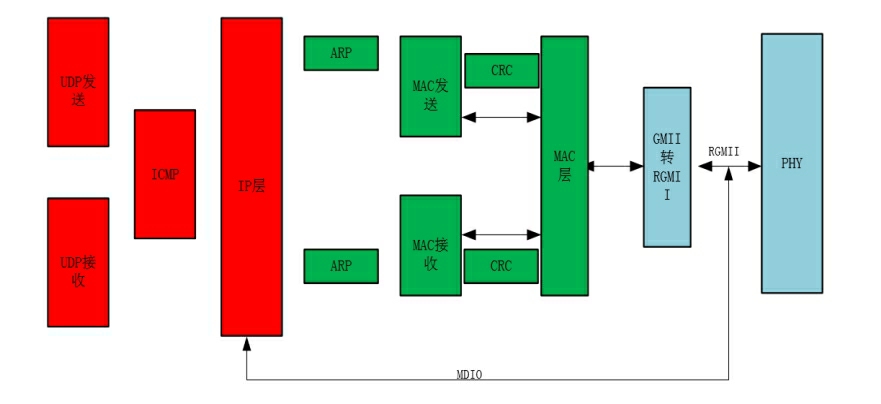

fpga rgmii接口以太网,支持udp,icmp,arp等协议在数字电路和网络通信领域,FPGA(现场可编程门阵列)一直扮演着重要角色。今天咱们就来唠唠基于 FPGA 的 RGMII 接口以太网,并且看看它是如何支持 UDP、ICMP 和 ARP 等常见网络协议的。

fpga rgmii接口以太网,支持udp,icmp,arp等协议

在数字电路和网络通信领域,FPGA(现场可编程门阵列)一直扮演着重要角色。今天咱们就来唠唠基于 FPGA 的 RGMII 接口以太网,并且看看它是如何支持 UDP、ICMP 和 ARP 等常见网络协议的。

RGMII 接口:以太网通信的桥梁

RGMII(Reduced Gigabit Media Independent Interface),即简化的千兆媒体独立接口,是一种常用于以太网物理层(PHY)和介质访问控制层(MAC)之间的接口标准。相比于其他接口,RGMII 以较少的引脚实现高速数据传输,对于 FPGA 资源利用来说非常友好。

FPGA 中 RGMII 接口设计要点

在 FPGA 设计 RGMII 接口时,主要涉及到时钟、数据和控制信号的处理。以 Verilog 代码为例:

module rgmii_interface (

input wire clk,

input wire rst,

// RGMII TX signals

output wire [3:0] tx_data,

output wire tx_ctl,

// RGMII RX signals

input wire [3:0] rx_data,

input wire rx_ctl

);

// 简单的 TX 数据寄存逻辑

reg [3:0] tx_data_reg;

always @(posedge clk or posedge rst) begin

if (rst) begin

tx_data_reg <= 4'b0000;

end else begin

// 这里假设从上层逻辑获取数据

tx_data_reg <= some_tx_data_source;

end

end

assign tx_data = tx_data_reg;

// TX 控制信号逻辑

reg tx_ctl_reg;

always @(posedge clk or posedge rst) begin

if (rst) begin

tx_ctl_reg <= 1'b0;

end else begin

// 根据传输状态决定控制信号

tx_ctl_reg <= some_tx_control_condition;

end

end

assign tx_ctl = tx_ctl_reg;

// RX 数据处理逻辑类似,为简洁省略部分

// 这里可以添加数据接收、校验等逻辑

reg [3:0] rx_data_reg;

always @(posedge clk or posedge rst) begin

if (rst) begin

rx_data_reg <= 4'b0000;

end else begin

rx_data_reg <= rx_data;

end

end

endmodule这段代码简单地展示了 RGMII 接口在 FPGA 中的信号处理方式。txdata 和 txctl 用于发送数据和控制信号,rxdata 和 rxctl 用于接收数据和控制信号。在实际应用中,sometxdatasource 和 sometxcontrolcondition 需要根据具体的上层逻辑和协议处理来定义。

UDP 协议:快速轻量的数据传输

UDP(User Datagram Protocol),用户数据报协议,以其简单、快速的特点广泛应用于实时性要求高但对数据准确性要求相对较低的场景,比如视频流、音频流传输。

UDP 在 FPGA 中的实现

在 FPGA 实现 UDP 协议,主要涉及 UDP 数据包的封装和解封装。以下是简化的 UDP 封装代码示例(依然以 Verilog 为例):

module udp_packet_encapsulation (

input wire clk,

input wire rst,

input wire [15:0] src_port,

input wire [15:0] dst_port,

input wire [15:0] length,

input wire [7:0] data_in,

output reg [7:0] udp_packet_out

);

reg [15:0] checksum;

// UDP 头部信息

reg [15:0] src_port_reg;

reg [15:0] dst_port_reg;

reg [15:0] length_reg;

always @(posedge clk or posedge rst) begin

if (rst) begin

src_port_reg <= 16'b0;

dst_port_reg <= 16'b0;

length_reg <= 16'b0;

checksum <= 16'b0;

end else begin

src_port_reg <= src_port;

dst_port_reg <= dst_port;

length_reg <= length;

// 简单的校验和计算,实际更复杂

checksum <= src_port + dst_port + length;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

udp_packet_out <= 8'b0;

end else begin

// 按顺序输出 UDP 头部和数据

case (udp_packet_counter)

0: udp_packet_out <= src_port_reg[15:8];

1: udp_packet_out <= src_port_reg[7:0];

// 依次类推输出其他头部字段和数据

endcase

end

end

endmodule这里的代码实现了 UDP 数据包的基本封装。srcport 和 dstport 分别是源端口和目的端口,length 是 UDP 数据包的长度。校验和的计算只是简单示意,实际应用中需要更复杂的算法来确保数据完整性。

ICMP 协议:网络诊断与控制

ICMP(Internet Control Message Protocol),网际控制报文协议,主要用于在 IP 主机、路由器之间传递控制消息,比如常见的 ping 命令就是基于 ICMP 协议。

FPGA 实现 ICMP 协议示例

module icmp_handler (

input wire clk,

input wire rst,

input wire [7:0] icmp_packet_in,

output reg [7:0] icmp_response_out

);

// 解析 ICMP 数据包类型和代码

reg [7:0] icmp_type;

reg [7:0] icmp_code;

always @(posedge clk or posedge rst) begin

if (rst) begin

icmp_type <= 8'b0;

icmp_code <= 8'b0;

end else begin

icmp_type <= icmp_packet_in[7:0];

icmp_code <= icmp_packet_in[15:8];

end

end

// 根据类型和代码生成响应

always @(posedge clk or posedge rst) begin

if (rst) begin

icmp_response_out <= 8'b0;

end else begin

if (icmp_type == 8'h08) begin // 假设是请求类型

// 构造响应数据包

icmp_response_out <= {8'h00, icmp_code}; // 简单回复

end

end

end

endmodule上述代码展示了如何在 FPGA 中处理 ICMP 数据包。首先解析接收到的 ICMP 数据包中的类型和代码,然后根据不同的类型(这里以请求类型为例)生成相应的响应。

ARP 协议:IP 与 MAC 地址的映射

ARP(Address Resolution Protocol),地址解析协议,用于将 IP 地址解析为 MAC 地址。在局域网中,设备通过 ARP 协议获取目标设备的 MAC 地址,以便进行数据传输。

FPGA 中的 ARP 实现思路

在 FPGA 实现 ARP 协议,需要维护一个 ARP 缓存表,用于存储 IP 地址和 MAC 地址的映射关系。以下是简单的缓存表操作代码示例:

module arp_cache (

input wire clk,

input wire rst,

input wire [31:0] ip_address,

input wire [47:0] mac_address,

input wire add_entry,

input wire lookup,

output reg [47:0] result_mac

);

// 简单的 ARP 缓存表,实际可扩展为更大容量

reg [47:0] arp_table [0:15];

reg [31:0] ip_table [0:15];

integer i;

always @(posedge clk or posedge rst) begin

if (rst) begin

for (i = 0; i < 16; i = i + 1) begin

arp_table[i] <= 48'b0;

ip_table[i] <= 32'b0;

end

end else if (add_entry) begin

for (i = 0; i < 16; i = i + 1) begin

if (ip_table[i] == 32'b0) begin

ip_table[i] <= ip_address;

arp_table[i] <= mac_address;

break;

end

end

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

result_mac <= 48'b0;

end else if (lookup) begin

for (i = 0; i < 16; i = i + 1) begin

if (ip_table[i] == ip_address) begin

result_mac <= arp_table[i];

break;

end

end

end

end

endmodule这段代码实现了一个简单的 ARP 缓存表。add_entry 信号用于添加新的 IP - MAC 映射关系到缓存表,lookup 信号用于根据给定的 IP 地址查找对应的 MAC 地址。

fpga rgmii接口以太网,支持udp,icmp,arp等协议

通过在 FPGA 中合理设计 RGMII 接口以及实现 UDP、ICMP 和 ARP 等协议,我们可以构建一个功能强大的以太网通信系统,满足不同应用场景的需求。无论是工业控制、网络设备还是物联网领域,这种基于 FPGA 的解决方案都有着广阔的应用前景。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)